MICROCHIP PIC24 Flash Programming

Impormasyon sa Produkto

Flash Programming

Ang dsPIC33/PIC24 nga mga pamilya sa mga device adunay internal programmable Flash program memory para sa pagpatuman sa user code. Adunay hangtod sa tulo ka mga pamaagi sa pagprograma niini nga memorya:

- Operasyon sa Instruksyon sa Table

- In-Circuit Serial Programming (ICSP)

- In-Application Programming (IAP)

Ang mga instruksyon sa lamesa naghatag ug pamaagi sa pagbalhin sa datos tali sa Flash program memory space ug sa data memory space sa dsPIC33/PIC24 device. Ang instruksiyon sa TBLRDL gigamit sa pagbasa gikan sa mga tipik [15:0] sa luna sa memorya sa programa. Ang instruksyon sa TBLWTL gigamit sa pagsulat sa mga tipik [15:0] sa Flash program memory space. Ang TBLRDL ug TBLWTL maka-access sa Flash program memory sa Word mode o Byte mode.

Dugang sa address sa memorya sa programa sa Flash, ang instruksyon sa lamesa nagtakda usab sa usa ka W register (o usa ka W Register Pointer sa usa ka lokasyon sa memorya), nga mao ang tinubdan sa data sa memorya sa Flash program nga isulat, o ang destinasyon alang sa usa ka Flash program. pagbasa sa memorya.

Kini nga seksyon naghulagway sa teknik sa pagprograma sa Flash program memory. Ang dsPIC33/ PIC24 nga mga pamilya sa mga device adunay internal programmable Flash program memory para sa pagpatuman sa user code. Adunay hangtod sa tulo ka mga pamaagi sa pagprograma niini nga memorya:

- Run-Time Self-Programming (RTSP)

- In-Circuit Serial Programming™ (ICSP™)

- Gipalambo nga In-Circuit Serial Programming (EICSP)

Ang RTSP gihimo sa software sa aplikasyon sa panahon sa pagpatuman, samtang ang ICSP ug EICSP gihimo gikan sa usa ka eksternal nga programmer gamit ang serial data connection sa device. Gitugotan sa ICSP ug EICSP ang labi ka paspas nga oras sa pagprograma kaysa RTSP. Ang mga teknik sa RTSP gihulagway sa Seksyon 4.0 "Run-Time Self-Programming (RTSP)". Ang mga protocol sa ICSP ug EICSP gihubit sa mga dokumento sa Programming Specification alang sa tagsa-tagsa nga mga himan, nga mahimong ma-download gikan sa Microchip weblugar (http://www.microchip.com). Kung nagprograma sa C nga lengguwahe, daghang mga built-in nga function ang magamit nga nagpadali sa Flash programming. Tan-awa ang “MPLAB® XC16 C Compiler User's Guide” (DS50002071) para sa mga detalye bahin sa mga built-in nga function.

Mga Instruksyon sa Paggamit sa Produkto

Aron maprograma ang Flash program memory, sunda kini nga mga lakang:

- Tan-awa ang device data sheet aron masusi kon ang family reference manual section nagsuporta sa device nga imong gigamit.

- I-download ang device data sheet ug family reference manual nga mga seksyon gikan sa Microchip Worldwide Website sa: http://www.microchip.com.

- Pagpili og usa sa tulo ka pamaagi sa pagprograma sa memorya (Table Instruction Operation, In-Circuit Serial Programming (ICSP), In-Application Programming (IAP)).

- Kung naggamit sa Table Instruction Operation, gamita ang instruksiyon sa TBLRDL sa pagbasa gikan sa bits[15:0] sa program memory space ug sa TBLWTL instruction sa pagsulat sa bits[15:0] sa Flash program memory space.

- Siguruha nga ipiho ang usa ka W register (o usa ka W Register Pointer sa usa ka lokasyon sa memorya) ingon nga gigikanan sa data sa memorya sa programa sa Flash nga isulat, o ang destinasyon alang sa usa ka pagbasa sa memorya sa Flash program.

Para sa dugang nga impormasyon ug mga detalye sa pagprograma sa Flash program memory, tan-awa ang dsPIC33/PIC24 Family Reference Manual.

TABLE INSTRUCTION OPERATION

Ang mga instruksyon sa lamesa naghatag ug pamaagi sa pagbalhin sa datos tali sa Flash program memory space ug sa data memory space sa dsPIC33/PIC24 device. Kini nga seksyon naghatag usa ka summary sa mga panudlo sa lamesa nga gigamit sa panahon sa pagprograma sa memorya sa programa sa Flash. Adunay upat ka sukaranan nga mga panudlo sa lamesa:

- TBLRDL: Ubos nga Gibasa sa Talaan

- TBLRDH: Taas nga Pagbasa sa Talaan

- TBLWTL: Talaan Isulat Ubos

- TBLWTH: Taas nga Pagsulat sa Talaan

Ang instruksiyon sa TBLRDL gigamit sa pagbasa gikan sa mga tipik [15:0] sa luna sa memorya sa programa. Ang instruksyon sa TBLWTL gigamit sa pagsulat sa mga tipik [15:0] sa Flash program memory space. Ang TBLRDL ug TBLWTL maka-access sa Flash program memory sa Word mode o Byte mode.

Ang mga instruksiyon sa TBLRDH ug TBLWTH gigamit sa pagbasa o pagsulat sa mga tipik [23:16] sa luna sa memorya sa programa. Ang TBLRDH ug TBLWTH maka-access sa Flash program memory sa Word o Byte mode. Tungod kay ang Flash program memory kay 24 bits lang ang gilapdon, ang TBLRDH ug TBLWTH nga mga instruksiyon makatubag sa taas nga byte sa Flash program memory nga wala. Kini nga byte gitawag nga "phantom byte". Ang bisan unsang pagbasa sa phantom byte mobalik 0x00. Ang pagsulat sa phantom byte walay epekto. Ang 24-bit Flash program memory mahimong isipon nga duha ka kilid nga 16-bit space, nga ang matag luna nag-ambit sa samang address range. Busa, ang mga instruksiyon sa TBLRDL ug TBLWTL nag-access sa "ubos" nga luna sa memorya sa programa (PM[15:0]). Ang mga instruksyon sa TBLRDH ug TBLWTH maka-access sa "taas" nga luna sa memorya sa programa (PM[31:16]). Ang bisan unsang pagbasa o pagsulat sa PM[31:24] maka-access sa phantom (wala gipatuman) nga byte. Kung ang bisan unsang mga instruksyon sa lamesa gigamit sa Byte mode, ang Least Significant bit (LSb) sa address sa lamesa gamiton isip byte select bit. Ang LSb nagtino kung unsang byte sa taas o ubos nga luna sa memorya sa programa ang ma-access.

Ang Figure 2-1 nag-ilustrar kung giunsa ang memorya sa programa sa Flash gitumong gamit ang mga instruksyon sa lamesa. Ang 24-bit program memory address naporma gamit ang bits[7:0] sa TBLPAG register ug ang Effective Address (EA) gikan sa W register nga gitakda sa table instruction. Ang 24-bit Program Counter (PC) gihulagway sa Figure 2-1 alang sa pakisayran. Ang taas nga 23 bits sa EA gigamit sa pagpili sa lokasyon sa memorya sa programa sa Flash.

Alang sa Byte mode table nga mga instruksyon, ang LSb sa W register EA gigamit sa pagpili kung unsang byte sa 16-bit Flash program memory word ang gitumong; Ang '1' nagpili sa mga bit [15:8] ug ang '0' nagpili sa mga bit [7:0]. Ang LSb sa W register EA wala tagda alang sa pagtudlo sa lamesa sa Word mode. Dugang sa address sa memorya sa programa sa Flash, ang instruksyon sa lamesa nagtakda usab sa usa ka W register (o usa ka W Register Pointer sa usa ka lokasyon sa memorya), nga mao ang tinubdan sa data sa memorya sa Flash program nga isulat, o ang destinasyon alang sa usa ka Flash program. pagbasa sa memorya. Alang sa operasyon sa pagsulat sa lamesa sa Byte mode, ang mga bits[15:8] sa tinubdan nga Working register wala tagda.

Paggamit sa Table Read Instructions

Ang pagbasa sa lamesa nanginahanglan duha ka lakang:

- Ang Address Pointer gipahimutang gamit ang TBLPAG register ug usa sa W registers.

- Mahimong mabasa ang sulud sa memorya sa programa sa Flash sa lokasyon sa adres.

- BASAHA WORD MODE

Ang code nga gipakita sa Example 2-1 ug ExampAng 2-2 nagpakita kon unsaon pagbasa ang pulong sa Flash program memory gamit ang mga instruksiyon sa lamesa sa Word mode.

- BASAHA ANG BYTE MODE

Ang code nga gipakita sa ExampAng le 2-3 nagpakita sa post-increment operator sa pagbasa sa ubos nga byte, nga maoy hinungdan nga ang adres sa Working register modugang sa usa. Gibutang niini ang EA[0] sa usa ka '1' alang sa pag-access sa tunga nga byte sa ikatulo nga panudlo sa pagsulat. Ang katapusan nga post-increment nagtakda sa W0 balik sa usa ka parehas nga adres, nga nagtudlo sa sunod nga lokasyon sa memorya sa programa sa Flash.

- TABLE WRITE LATCHES

Ang mga instruksyon sa pagsulat sa lamesa dili direktang isulat sa nonvolatile nga memorya sa programa. Hinuon, ang mga panudlo sa pagsulat sa lamesa nagkarga sa mga trangka sa pagsulat nga nagtipig sa datos sa pagsulat. Ang mga rehistro sa NVM Address kinahanglan nga makarga sa unang adres diin kinahanglan nga isulat ang mga latched data. Kung nakarga na ang tanan nga mga trangka sa pagsulat, ang aktuwal nga operasyon sa pagprograma sa memorya gisugdan pinaagi sa pagpatuman sa usa ka espesyal nga han-ay sa mga panudlo. Atol sa pagprograma, gibalhin sa hardware ang datos sa mga write latches sa Flash memory. Ang write latches kanunay magsugod sa address 0xFA0000, ug molugway sa 0xFA0002 para sa word programming, o pinaagi sa 0xFA00FE para sa mga device nga adunay row programming.

Mubo nga sulat: Ang gidaghanon sa pagsulat latches managlahi sa device. Tan-awa ang “Flash Program Memory” nga kapitulo sa espesipikong device data sheet alang sa gidaghanon sa magamit nga write latches.

MGA REGISTER SA PAGKONTROL

Pipila ka Espesyal nga Function Registers (SFRs) ang gigamit sa pagprograma sa Flash program memory erase ug write operations: NVMCON, NVMKEY, ug ang NVM Address registers, NVMADR ug NVMADRU.

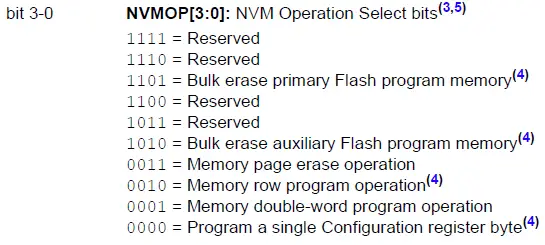

Register sa NVMCON

Ang rehistro sa NVMCON mao ang nag-unang rehistro sa pagkontrol alang sa Flash ug mga operasyon sa programa/pagpapas. Kini nga rehistro nagpili kung ang usa ka pagpapas o operasyon sa programa himuon ug mahimo’g magsugod ang programa o cycle sa pagpapas. Ang rehistro sa NVMCON gipakita sa Register 3-1. Ang ubos nga byte sa NVMCON nag-configure sa matang sa NVM nga operasyon nga ipahigayon.

Pagrehistro sa NVMKEY

Ang NVMKEY register (tan-awa ang Register 3-4) kay write-only register nga gigamit sa pagpugong sa aksidenteng pagsulat sa NVMCON nga makadaut sa Flash memory. Kung maablihan na, ang pagsulat sa NVMCON gitugotan alang sa usa ka siklo sa panudlo diin ang WR bit mahimong itakda aron magamit ang usa ka pagpapas o rutina sa programa. Tungod sa mga kinahanglanon sa oras, gikinahanglan ang pag-disable sa mga interrupt.

Buhata ang mosunod nga mga lakang sa pagsugod sa usa ka erase o programming sequence:

- I-disable ang mga interrupt.

- Isulat ang 0x55 sa NVMKEY.

- Isulat ang 0xAA sa NVMKEY.

- Sugdi ang programming write cycle pinaagi sa pagbutang sa WR bit (NVMCON[15]).

- Ipatuman ang duha ka instruksiyon sa NOP.

- Iuli ang mga interrupt.

PAG-DISABLING SA MGA PAGBABAG

Ang pag-disable sa mga interrupt gikinahanglan para sa tanang operasyon sa Flash aron masiguro ang malampusong resulta. Kung adunay usa ka interrupt nga mahitabo sa panahon sa NVMKEY unlock sequence, kini makababag sa pagsulat sa WR bit. Ang NVMKEY unlock sequence kinahanglang ipatuman nga walay hunong, sama sa gihisgutan sa Seksyon 3.2 "NVMKEY Register".

Ang mga interrupt mahimong ma-disable sa usa sa duha ka mga pamaagi, pinaagi sa pag-disable sa Global Interrupt Enable (GIE bit), o pinaagi sa paggamit sa instruksiyon sa DSI. Ang instruksiyon sa DSI wala girekomendar tungod kay kini nag-disable lamang sa mga interrupts sa Priority 6 o ubos; busa, ang Global Interrupt Enable nga pamaagi kinahanglang gamiton.

Ang CPU nagsulat sa GIE magkuha og duha ka mga siklo sa pagtudlo sa dili pa makaapekto sa dagan sa code. Duha ka NOP nga instruksyon ang gikinahanglan pagkahuman, o mahimong pulihan sa bisan unsang ubang mapuslanon nga instruksyon sa trabaho, sama sa pagkarga sa NVMKEY; kini magamit sa set ug klaro nga mga operasyon. Ang pag-amping kinahanglan buhaton kung ang pag-re-enable sa mga interrupts aron ang NVM nga gipunting nga rutina dili motugot sa mga interrupts kung ang usa ka nauna nga gitawag nga function nakapugong niini alang sa ubang mga hinungdan. Aron matubag kini sa Assembly, ang usa ka stack push ug pop mahimong magamit aron mapadayon ang kahimtang sa GIE bit. Sa C, ang usa ka variable sa RAM mahimong magamit sa pagtipig sa INTCON2 sa wala pa ang paglimpyo sa GIE. Gamita ang mosunod nga han-ay aron ma-disable ang mga interrupt:

- Iduso ang INTCON2 ngadto sa stack.

- Hawani ang GIE bit.

- Duha ka NOP o pagsulat sa NVMKEY.

- Sugdi ang programming cycle pinaagi sa pag-set sa WR bit (NVMCON[15]).

- Ibalik ang kahimtang sa GIE pinaagi sa POP sa INTCON2.

Mga Rehistro sa NVM Address

Ang duha ka NVM Address nga mga rehistro, NVMADRU ug NVMADR, kon magkadugtong, maporma ang 24-bit EA sa pinili nga laray o pulong alang sa mga operasyon sa programming. Ang NVMADRU nga rehistro gigamit sa paghawid sa ibabaw nga walo ka bits sa EA, ug ang NVMADR nga rehistro gigamit sa paghawid sa ubos nga 16 ka bits sa EA. Ang ubang mga himan mahimong magtumong niining sama nga mga rehistro sama sa NVMADRL ug NVMADRH. Ang mga rehistro sa NVM Address kinahanglan kanunay nga magpunting sa usa ka double instruction word boundary sa diha nga maghimo sa usa ka double instruction word programming operation, usa ka row boundary sa diha nga nagpahigayon sa usa ka row programming operation o usa ka page boundary sa dihang naghimo sa usa ka page erase operation.

Register 3-1: NVMCON: Flash Memory Control Register

Nota

- Kini nga gamay mahimo lamang nga i-reset (ie, cleared) sa usa ka Power-on Reset (POR).

- Kung mogawas sa Idle mode, adunay usa ka power-up delay (TVREG) sa dili pa magamit ang memorya sa programa sa Flash. Tan-awa ang “Mga Kinaiya sa Elektrisidad” nga kapitulo sa espesipikong panid sa datos sa device alang sa dugang impormasyon.

- Ang tanan nga uban nga mga kombinasyon sa NVMOP[3:0] wala gipatuman.

- Kini nga pagpaandar dili magamit sa tanan nga mga aparato. Tan-awa ang “Flash Program Memory” nga kapitulo sa espesipikong device data sheet alang sa mga magamit nga operasyon.

- Ang pagsulod sa power-saving mode human sa pagpatuman sa instruksiyon sa PWRSAV nagdepende sa pagkompleto sa tanang pending nga operasyon sa NVM.

- Kini nga gamay anaa lamang sa mga himan nga nagsuporta sa RAM buffered row programming. Tan-awa ang data sheet nga espesipiko sa device alang sa pagkaanaa.

Nota

- Kini nga gamay mahimo lamang nga i-reset (ie, cleared) sa usa ka Power-on Reset (POR).

- Kung mogawas sa Idle mode, adunay usa ka power-up delay (TVREG) sa dili pa magamit ang memorya sa programa sa Flash. Tan-awa ang “Mga Kinaiya sa Elektrisidad” nga kapitulo sa espesipikong panid sa datos sa device alang sa dugang impormasyon.

- Ang tanan nga uban nga mga kombinasyon sa NVMOP[3:0] wala gipatuman.

- Kini nga pagpaandar dili magamit sa tanan nga mga aparato. Tan-awa ang “Flash Program Memory” nga kapitulo sa espesipikong device data sheet alang sa mga magamit nga operasyon.

- Ang pagsulod sa power-saving mode human sa pagpatuman sa instruksiyon sa PWRSAV nagdepende sa pagkompleto sa tanang pending nga operasyon sa NVM.

- Kini nga gamay anaa lamang sa mga himan nga nagsuporta sa RAM buffered row programming. Tan-awa ang data sheet nga espesipiko sa device alang sa pagkaanaa.

Register 3-2: NVMADRU: Nonvolatile Memory Upper Address Register

Register 3-3: NVMADR: Nonvolatile Memory Address Register

Register 3-4: NVMKEY: Nonvolatile Memory Key Register

RUN-TIME SELF-PROGRAMMING (RTSP)

Gitugotan sa RTSP ang aplikasyon sa gumagamit nga usbon ang sulud sa memorya sa programa sa Flash. Ang RTSP gihimo gamit ang TBLRD (Table Read) ug TBLWT (Table Write) nga mga instruksyon, ang TBLPAG register, ug ang NVM Control registers. Uban sa RTSP, ang user nga aplikasyon makapapas sa usa ka panid sa Flash memory ug programa sa duha ka instruksiyon nga mga pulong o hangtod sa 128 ka instruksiyon nga mga pulong sa pipila ka mga himan.

Operasyon sa RTSP

The dsPIC33/PIC24 Flash program memory array is organized into erase pages that can contain up to 1024 instructions. The double-word programming option is available in all devices in the dsPIC33/PIC24 families. In addition, certain devices have row programming capability, which allows the programming of up to 128 instruction words at a time. Programming and erase operations always occur on an even double programming word, row or page boundaries. Refer to the “Flash Program Memory” chapter of the specific device data sheet for the availability and sizes of a programming row, and the page size for erasing. The Flash program memory implements holding buffers, called write latches, that can contain up to 128 instructions of programming data depending on the device. Prior to the actual programming operation, the write data must be loaded into the write latches. The basic sequence for RTSP is to set up the Table Pointer, TBLPAG register, and then perform a series of TBLWT instructions to load the write latches. Programming is performed by setting the control bits in the NVMCON register. The number of TBLWTL and TBLWTH instructions needed to load the write latches is equal to the number of program words to be written.

Mubo nga sulat: Girekomenda nga ang rehistro sa TBLPAG i-save sa wala pa ang pagbag-o ug ibalik pagkahuman magamit.

PAHINUMDOM

Sa pipila ka mga himan, ang Configuration bits gitipigan sa katapusang panid sa programa nga Flash user memory space sa usa ka seksyon nga gitawag, "Flash Configuration Bytes". Uban niini nga mga himan, ang paghimo sa usa ka panid sa pagtangtang sa operasyon sa katapusang panid sa panumduman sa programa mopapas sa Flash Configuration bytes, nga makapahimo sa pagpanalipod sa code. Busa, ang mga tiggamit dili kinahanglan nga mohimo sa mga operasyon sa pagtangtang sa panid sa katapusang panid sa memorya sa programa. Dili kini kabalaka kung ang mga tipik sa Configuration gitipigan sa wanang sa memorya sa Configuration sa usa ka seksyon nga gitawag, "Mga Rehistro sa Pag-configure sa Device". Tan-awa ang Program Memory Map sa “Memory Organization” nga kapitulo sa espesipikong device data sheet aron mahibal-an kung asa nahimutang ang Configuration bits.

Mga Operasyon sa Flash Programming

A program or erase operation is necessary for programming or erasing the internal Flash program memory in RTSP mode. The program or erase operation is automatically timed by the device (refer to the specific device data sheet for timing information). Setting the WR bit (NVMCON[15]) starts the operation. The WR bit is automatically cleared when the operation is finished. The CPU stalls until the programming operation is finished. The CPU will not execute any instructions or respond to interrupts during this time. If any interrupts occur during the programming cycle, they will remain pending until the cycle completes. Some dsPIC33/PIC24 devices may provide auxiliary Flash program memory (refer to the “Memory Organization” chapter of the specific device data sheet for details), which allows instruction execution without CPU Stalls while user Flash program memory is being erased and/ or programmed. Conversely, auxiliary Flash program memory can be programmed without CPU Stalls, as long as code is executed from the user Flash program memory. The NVM interrupt can be used to indicate that the programming operation is complete.

Nota

- Kung mahitabo ang POR o BOR nga panghitabo samtang ang RTSP erase o programming operation nagpadayon, ang RTSP operation i-abort dayon. Kinahanglang ipatuman pag-usab sa user ang operasyon sa RTSP human makagawas ang device sa Reset.

- Kung ang EXTR, SWR, WDTO, TRAPR, CM o IOPUWR Reset nga panghitabo mahitabo samtang ang RTSP erase o programming operation nagpadayon, ang device i-reset lang human makompleto ang RTSP operation.

RTSP PROGRAMMING ALGORITHM

Kini nga seksyon naghulagway sa RTSP programming, nga naglangkob sa tulo ka dagkong mga proseso.

Paghimo og RAM Image sa Data Page nga Usbon

Buhata kining duha ka mga lakang sa paghimo og RAM nga imahe sa data page nga usbon:

- Basaha ang panid sa Flash program memory ug tipigi kini sa data RAM isip usa ka data nga "imahe". Kinahanglang basahon ang imahe sa RAM sugod sa utlanan sa adres sa panid.

- Usba ang imahe sa data sa RAM kung gikinahanglan.

Erasing Flash Program Memory

Human makompleto ang mga Lakang 1 ug 2 sa ibabaw, himoa ang mosunod nga upat ka mga lakang aron papason ang Flash program memory page:

- Itakda ang NVMOP[3:0] bits (NVMCON[3:0]) aron papason ang panid sa Flash program memory nga gibasa gikan sa Step 1.

- Isulat ang sugod nga adres sa panid nga papason sa NVMADRU ug NMVADR nga mga rehistro.

- Uban sa mga interrupts disabled:

- a) Isulat ang yawe nga han-ay sa NVMKEY register aron makahimo sa pag-set sa WR bit (NVMCON[15]).

- b) Ibutang ang WR bit; kini magsugod sa erase cycle.

- c) Ipatuman ang duha ka instruksiyon sa NOP.

- Ang WR bit ma-clear kung kompleto na ang erase cycle.

Pagprograma sa Flash Memory Page

Ang sunod nga bahin sa proseso mao ang pagprograma sa Flash memory page. Ang panid sa Flash memory giprograma gamit ang datos gikan sa imahe nga gihimo sa Lakang 1. Ang datos gibalhin ngadto sa pagsulat nga mga trangka sa mga pag-uswag sa duha ka mga pulong sa instruksiyon o mga laray. Ang tanan nga mga aparato adunay doble nga instruksiyon nga katakus sa pagprograma sa pulong. (Tan-awa ang "Flash Program Memory" nga kapitulo sa espesipikong device data sheet aron mahibal-an kung, ug unsa nga matang sa, row programming ang anaa.) Human makarga ang mga write latches, ang programming operation gisugdan, nga nagbalhin sa datos gikan sa isulat ang mga trangka sa Flash memory. Kini gisubli hangtud nga ang tibuok panid maprograma. Balika ang mosunod nga tulo ka mga lakang, sugod sa unang instruksyon nga pulong sa Flash nga panid ug pagdugang sa mga lakang sa doble nga mga pulong sa programa, o mga linya sa instruksiyon, hangtud nga ang tibuok panid maprograma:

- I-load ang mga trangka sa pagsulat:

- a) Ibutang ang rehistro sa TBLPAG aron itudlo ang lokasyon sa mga write latches.

- b) I-load ang gusto nga gidaghanon sa mga trangka gamit ang mga pares sa TBLWTL ug TBLWTH nga mga instruksyon:

- Para sa double-word programming, duha ka pares sa TBLWTL ug TBLWTH nga mga instruksiyon ang gikinahanglan

- Para sa row programming, gikinahanglan ang usa ka pares sa TBLWTL ug TBLWTH nga mga instruksiyon para sa matag instruksiyon nga word row element.

- Pagsugod sa operasyon sa programming:

- a) I-set ang NVMOP[3:0] bits (NVMCON[3:0]) para magprograma ug doble nga instruksiyon nga mga pulong o usa ka laray sa instruksiyon, kon angay.

b) Isulat ang unang adres sa dobleng instruksiyon nga pulong o linya sa instruksiyon nga iprograma sa NVMADRU ug NVMADR nga mga rehistro.

c) Uban sa mga interrupts nga gibabagan:

• Isulat ang yawe nga han-ay sa NVMKEY register aron makahimo sa pag-set sa WR bit (NVMCON[15])

• Ibutang ang WR bit; kini magsugod sa erase cycle

• Ipatuman ang duha ka instruksiyon sa NOP

- a) I-set ang NVMOP[3:0] bits (NVMCON[3:0]) para magprograma ug doble nga instruksiyon nga mga pulong o usa ka laray sa instruksiyon, kon angay.

- Ang WR bit ma-clear kung kompleto na ang siklo sa programming.

Balika ang tibuok proseso kon gikinahanglan aron maprograma ang gusto nga gidaghanon sa memorya sa programa sa Flash.

Nota

- Kinahanglan nga hinumdoman sa user nga ang minimum nga kantidad sa memorya sa programa sa Flash nga mahimong mapapas gamit ang RTSP usa ka panid nga gipapas sa singe. Busa, importante nga ang usa ka imahen niini nga mga lokasyon tipigan sa kinatibuk-ang katuyoan nga RAM sa dili pa magsugod ang usa ka siklo sa pagpapas.

- Ang usa ka laray o pulong sa Flash program memory kinahanglan dili maprograma labaw pa sa kaduha sa dili pa mapapas.

- Sa mga device nga adunay Configuration bytes nga gitipigan sa kataposang panid sa Flash, ang pagpahigayon ug page erase operation sa kataposang panid sa memorya sa programa motangtang sa Configuration bytes, nga makapanalipod sa code. Sa kini nga mga aparato, ang katapusan nga panid sa Flash memory kinahanglan dili mapapas.

ERASING ONE PAGE OF FLASH

Ang han-ay sa code nga gipakita sa Example 4-1 mahimong gamiton sa pagpapas sa usa ka panid sa Flash program memory. Ang rehistro sa NVMCON gi-configure aron mapapas ang usa ka panid sa memorya sa programa. Ang NVMADR ug NMVADRU nga mga rehistro gikargahan sa sinugdanan nga adres sa panid nga papason. Ang memorya sa programa kinahanglan nga mapapas sa usa ka "even" page address boundary. Tan-awa ang “Flash Program Memory” nga kapitulo sa espesipikong device data sheet aron matino ang gidak-on sa Flash page.

Ang pagpapas nga operasyon gisugdan pinaagi sa pagsulat sa usa ka espesyal nga unlock, o yawe nga han-ay, ngadto sa NVMKEY register sa wala pa i-set ang WR bit (NVMCON[15]). Ang han-ay sa pag-abli kinahanglan nga ipatuman sa eksaktong pagkasunod-sunod, sama sa gipakita sa Example 4-1, walay hunong; busa, ang mga interrupts kinahanglang i-disable.

Duha ka NOP nga instruksyon ang kinahanglang isulod sa code human sa erase cycle. Sa pipila ka mga device, ang Configuration bits gitipigan sa kataposang panid sa Flash program. Uban niini nga mga himan, ang paghimo sa usa ka page erase operation sa katapusang pahina sa memorya sa programa mopapas sa Flash Configuration bytes, nga makapahimo sa pagpanalipod sa code isip resulta. Ang mga tiggamit kinahanglan nga dili mohimo sa mga operasyon sa pagtangtang sa panid sa katapusang panid sa memorya sa programa.

NAG-LOAD SA PAGSULAT NGA MGA TALA

Ang mga write latches kay gigamit isip storage mechanism tali sa user application Table Writes ug sa aktuwal nga programming sequence. Atol sa operasyon sa programming, ibalhin sa device ang datos gikan sa mga write latches ngadto sa Flash memory. Alang sa mga himan nga nagsuporta sa row programming, ExampAng 4-3 nagpakita sa han-ay sa mga instruksyon nga magamit sa pagkarga sa 128 ka mga trangka sa pagsulat (128 ka mga pulong sa instruksiyon). Ang 128 TBLWTL ug 128 TBLWTH nga mga instruksyon gikinahanglan aron makarga ang mga write latches alang sa pagprograma sa usa ka laray sa Flash program memory. Tan-awa ang "Flash Program Memory" nga kapitulo sa espesipikong device data sheet aron mahibal-an ang gidaghanon sa mga programming latches nga anaa sa imong device. Alang sa mga himan nga dili mosuporta sa row programming, Example 4-4 nagpakita sa han-ay sa mga instruksyon nga mahimong gamiton sa pagkarga sa duha ka pagsulat trangka (duha ka instruksiyon nga mga pulong). Duha ka TBLWTL ug duha ka TBLWTH nga instruksyon ang gikinahanglan aron makarga ang mga write latches.

Nota

- Ang code alang sa Load_Write_Latch_Row gipakita sa Example 4-3 ug ang code para sa Load_Write_Latch_Word gipakita sa Exampug 4-4. Ang code sa duha niini nga examples ang gihisgotan sa sunod nga examples.

- Tan-awa ang piho nga data sheet sa aparato alang sa gidaghanon sa mga trangka.

SINGLE ROW PROGRAMMING EXAMPLE

Ang rehistro sa NVMCON gi-configure aron magprograma sa usa ka laray sa memorya sa programa sa Flash. Ang operasyon sa programa gisugdan pinaagi sa pagsulat sa usa ka espesyal nga pag-abli, o yawe nga han-ay, ngadto sa NVMKEY register sa dili pa ibutang ang WR bit (NVMCON[15]). Ang han-ay sa pag-abli kinahanglan nga ipatuman nga walay paghunong, ug sa eksaktong pagkasunod-sunod, sama sa gipakita sa Exampug 4-5. Busa, ang mga interrupts kinahanglang i-disable sa dili pa isulat ang han-ay.

Mubo nga sulat: Dili tanan nga mga aparato adunay kapabilidad sa pagprograma sa linya. Tan-awa ang "Flash Program Memory" nga kapitulo sa espesipikong device data sheet aron mahibal-an kung kini nga opsyon anaa ba.

Duha ka NOP nga instruksyon ang kinahanglang isulod sa code human sa programming cycle.

ROW PROGRAMMING GAMIT ANG RAM BUFFER

Pilia ang dsPIC33 nga mga himan nga nagtugot sa row programming nga ipahigayon direkta gikan sa buffer space sa data RAM, imbes nga moagi sa holding latches aron mabalhin ang data gamit ang TBLWT instructions. Ang lokasyon sa RAM buffer gitino pinaagi sa NVMSRCADR register(s), nga puno sa data RAM address nga naglangkob sa unang pulong sa data sa programa nga isulat.

Sa wala pa ipahigayon ang operasyon sa programa, ang buffer space sa RAM kinahanglan nga puno sa laray sa datos nga maprograma. Ang RAM mahimong ma-load sa bisan usa ka compressed (packed) o uncompressed format. Ang compressed storage naggamit og usa ka pulong nga datos aron tipigan ang Most Significant Bytes (MSBs) sa duha ka kasikbit nga mga pulong sa datos sa programa. Ang wala ma-compress nga format naggamit ug duha ka pulong nga datos alang sa matag pulong sa datos sa programa, nga ang taas nga byte sa matag laing pulong mao ang 00h. Ang compressed format naggamit ug mga 3/4 sa space sa data RAM kumpara sa uncompressed format. Ang uncompressed format, sa laing bahin, nagsundog sa istruktura sa 24-bit program data word, kompleto sa taas nga phantom byte. Ang format sa datos gipili sa RPDF bit (NVMCON[9]). Kining duha ka pormat gipakita sa Figure 4-1.

Sa higayon nga ma-load ang RAM buffer, ang Flash Address Pointers, NVMADR ug NVMADRU, gikargahan sa 24-bit start address sa Flash row nga isulat. Sama sa pagprograma sa mga write latches, ang proseso gisugdan pinaagi sa pagsulat sa NVM unlock sequence, gisundan sa pagbutang sa WR bit. Kung gisugdan, ang aparato awtomatik nga nagkarga sa husto nga mga trangka ug gidugangan ang mga rehistro sa NVM Address hangtod nga naprograma ang tanan nga mga byte. Example 4-7 nagpakita ug example sa proseso. Kung ang NVMSRCADR gibutang sa usa ka kantidad nga ang usa ka data underrun error nga kahimtang mahitabo, ang URERR bit (NVMCON[8]) ibutang aron ipakita ang kondisyon.

Ang mga device nga nag-implementar sa RAM buffer row programming nagpatuman usab og usa o duha ka write latches. Gikarga kini gamit ang mga instruksyon sa TBLWT ug gigamit sa paghimo sa mga operasyon sa word programming.

PAGPROGRAMA SA PULONG

Ang rehistro sa NVMCON gi-configure aron magprograma sa duha nga mga pulong sa panudlo sa memorya sa programa sa Flash. Ang operasyon sa programa gisugdan pinaagi sa pagsulat sa usa ka espesyal nga pag-abli, o yawe nga han-ay, ngadto sa NVMKEY register sa dili pa ibutang ang WR bit (NVMCON[15]). Ang han-ay sa pag-abli kinahanglan nga ipatuman sa eksaktong pagkasunod-sunod, sama sa gipakita sa Example 4-8, walay hunong. Busa, ang mga interrupt kinahanglan nga dili ma-disable sa dili pa isulat ang han-ay.

Duha ka NOP nga instruksyon ang kinahanglang isulod sa code human sa programming cycle.

Pagsulat sa Device Configuration Registers

Sa pipila ka mga himan, ang mga tipik sa Configuration gitipigan sa wanang sa memorya sa pag-configure sa usa ka seksyon nga gitawag, "Mga Rehistro sa Pag-configure sa Device". Sa ubang mga device, ang Configuration bits gitipigan sa kataposang panid sa programa Flash user memory space sa usa ka seksyon nga gitawag og, “Flash Configuration Bytes”. Uban niini nga mga himan, ang paghimo sa usa ka panid sa pagtangtang sa operasyon sa katapusang panid sa panumduman sa programa mopapas sa Flash Configuration bytes, nga makapahimo sa pagpanalipod sa code. Busa, ang mga tiggamit dili kinahanglan nga mohimo sa mga operasyon sa pagtangtang sa panid sa katapusang panid sa memorya sa programa. Tan-awa ang Program Memory Map sa “Memory Organization” nga kapitulo sa espesipikong device data sheet aron mahibal-an kung asa nahimutang ang Configuration bits.

Sa diha nga ang Configuration bits gitipigan sa configuration memory space, ang RTSP mahimong gamiton sa pagsulat ngadto sa device Configuration registers, ug RTSP nagtugot sa matag Configuration register nga tagsa-tagsa nga isulat pag-usab nga dili una maghimo ug erase cycle. Kinahanglan nga mag-amping kung isulat ang mga rehistro sa Configuration tungod kay gikontrol nila ang kritikal nga mga parameter sa pag-operate sa aparato, sama sa gigikanan sa orasan sa sistema, pagpagana sa PLL ug WDT.

Ang pamaagi sa pagprograma sa usa ka device Configuration register susama sa pamaagi sa pagprograma sa Flash program memory, gawas nga ang TBLWTL instructions lang ang gikinahanglan. Kini tungod kay ang ibabaw nga walo ka bits sa matag device Configuration register wala magamit. Dugang pa, ang bit 23 sa Address sa Pagsulat sa Talaan kinahanglan nga itakda aron ma-access ang mga rehistro sa Configuration. I-refer ang “Device Configuration” (DS70000618) sa “dsPIC33/PIC24 Family Reference Manual” ug ang “Special Features” nga chapter sa specific device data sheet para sa tibuok deskripsyon sa device Configuration registers.

Nota

- Ang pagsulat sa mga rehistro sa Configuration sa aparato dili magamit sa tanan nga mga aparato. Tan-awa ang “Special Features” nga kapitulo sa espesipikong device data sheet aron matino ang mga mode nga anaa sumala sa device-specific NVMOP[3:0] bits' definition.

- Samtang nagpahigayon sa RTSP sa mga rehistro sa Configuration sa aparato, ang aparato kinahanglan nga molihok gamit ang internal nga FRC Oscillator (walay PLL). Kung ang aparato naglihok gikan sa lahi nga gigikanan sa orasan, usa ka switch sa orasan sa internal nga FRC Oscillator (NOSC [2: 0] = 000) kinahanglan himuon sa wala pa ipahigayon ang operasyon sa RTSP sa mga rehistro sa Configuration sa aparato.

- Kung ang Primary Oscillator Mode Select bits (POSCMD[1:0]) sa Oscillator Configuration register (FOSC) giprograma pag-usab sa usa ka bag-ong bili, ang user kinahanglang mosiguro nga ang Clock Switching Mode bits (FCKSM[1:0]) sa ang rehistro sa FOSC adunay inisyal nga giprograma nga kantidad nga '0', sa wala pa ipahigayon kini nga operasyon sa RTSP.

CONFIGURATION REGISTER WRITE ALGORITHM

Ang kinatibuk-ang pamaagi mao ang mosunod:

- Isulat ang bag-ong kantidad sa configuration sa Table Write latch gamit ang instruksiyon sa TBLWTL.

- I-configure ang NVMCON para sa usa ka Configuration register write (NVMCON = 0x4000).

- Isulat ang adres sa Configuration register nga iprograma sa NVMADRU ug NVMADR registers.

- I-disable ang mga interrupt, kung mahimo.

- Isulat ang yawe nga han-ay sa NVMKEY register.

- Sugdi ang han-ay sa pagsulat pinaagi sa pagbutang sa WR bit (NVMCON[15]).

- I-enable pag-usab ang mga interrupt, kon gikinahanglan.

ExampAng 4-10 nagpakita sa han-ay sa code nga mahimong gamiton sa pag-usab sa usa ka device Configuration register.

REGISTER MAPA

Usa ka summary sa mga rehistro nga nalangkit sa Flash Programming gihatag sa Table 5-1.

Kini nga seksyon naglista sa mga nota sa aplikasyon nga may kalabutan niini nga seksyon sa manwal. Kini nga mga nota sa aplikasyon mahimong dili espesipikong isulat alang sa mga pamilya sa produkto nga dsPIC33/PIC24, apan ang mga konsepto kay may kalabotan ug mahimong gamiton uban ang kausaban ug posible nga mga limitasyon. Ang kasamtangan nga mga nota sa aplikasyon nga may kalabutan sa Flash Programming mao ang:

Mubo nga sulat: Palihug bisitaha ang Microchip weblugar (www.microchip.com) para sa dugang nga mga Nota sa Aplikasyon ug code examples alang sa dsPIC33/PIC24 nga mga pamilya sa mga device.

KASAYSAYAN SA REBISYON

Rebisyon A (Agosto 2009)

Kini ang inisyal nga gipagawas nga bersyon niini nga dokumento.

Rebisyon B (Pebrero 2011)

Kini nga rebisyon naglakip sa mosunod nga mga update:

- Examples:

- Gitangtang Example 5-3 ug Exampsa 5-4

- Gi-update nga Exampug 4-1, Example 4-5 ug Exampsa 4-10

- Ang bisan unsang mga pakisayran sa #WR gi-update sa #15 sa Exampug 4-1, Example 4-5 ug Exampsa 4-8

- Gi-update ang mosunod sa Exampug 4-3:

- Gi-update ang titulo nga "Word Programming" ngadto sa "Loading Write Latches for Row Programming"

- Ang bisan unsang paghisgot sa #ram_image gi-update sa #0xFA

- Gidugang Exampsa 4-4

- Gi-update ang titulo sa Exampsa 4-8

- Mubo nga sulat:

- Gidugang ang duha ka mga nota sa Seksyon 4.2 "Flash Programming Operations"

- Gi-update ang nota sa Seksyon 4.5.2 "Pagkarga sa Pagsulat sa mga Latch"

- Gidugang ang tulo ka mga nota sa Seksyon 4.6 "Pagsulat sa Mga Rehistro sa Pag-configure sa Device"

- Gidugang ang Note 1 sa Table 5-1

- Mga rehistro:

- Gi-update ang bit value para sa NVMOP[3:0]: NVM Operation Pagpili og mga bit sa Flash Memory Control (NVMCON) register (tan-awa ang Register 3-1)

- Mga Seksyon:

- Gitangtang ang mga seksyon 5.2.1.4 "Pagsulat sa Pulong Mode" ug 5.2.1.5 "Pagsulat Byte Mode"

- Gi-update nga Seksyon 3.0 "Mga Rehistro sa Pagkontrol"

- Gi-update ang mosunod sa Seksyon 4.5.5 "Pagprograma sa Pulong":

- Giusab ang titulo sa seksyon nga "Pagprograma sa Usa ka Pulong sa Flash Memory" ngadto sa "Pagprograma sa Pulong"

- Gi-update ang unang paragraph

- Giusab ang mga termino nga "usa ka pulong" ngadto sa "usa ka parisan sa mga pulong" sa ikaduhang parapo

- Gidugang ang bag-ong Lakang 1 sa Seksyon 4.6.1 "Pagrehistro sa Pag-configure sa Pagsulat sa Algoritma"

- Mga lamesa:

- Gi-update nga Talaan 5-1

- Ang pipila ka mga pakisayran sa memorya sa programa gi-update sa Flash program memory

- Ang ubang mga menor de edad nga pag-update sama sa lengguwahe ug pag-format sa mga update gilakip sa tibuuk nga dokumento

Rebisyon C (Hunyo 2011)

Kini nga rebisyon naglakip sa mosunod nga mga update:

- Examples:

- Gi-update nga Exampsa 4-1

- Gi-update nga Exampsa 4-8

- Mubo nga sulat:

- Gidugang usa ka nota sa Seksyon 4.1 "Operasyon sa RTSP"

- Gidugang Note 3 sa Seksyon 4.2 "Flash Programming Operations"

- Gidugang ang Note 3 sa Seksyon 4.2.1 "RTSP Programming Algorithm"

- Added a note in Section 4.5.1 “Erasing One Page of Flash”

- Gidugang nga Nota 2 sa Seksyon 4.5.2 "Pagkarga sa Pagsulat sa mga Latch"

- Mga rehistro:

- Gi-update ang gamay nga paghulagway alang sa mga bit 15-0 sa Nonvolatile Memory Address register (tan-awa ang Register 3-3)

- Mga Seksyon:

- Gi-update nga Seksyon 4.1 "Operasyon sa RTSP"

- Gi-update nga Seksyon 4.5.5 "Pagprograma sa Pulong"

- Ang ubang mga menor de edad nga pag-update sama sa lengguwahe ug pag-format sa mga update gilakip sa tibuuk nga dokumento

Rebisyon D (Disyembre 2011)

Kini nga rebisyon naglakip sa mosunod nga mga update:

- Gi-update nga Seksyon 2.1.3 "Table Write Latches"

- Gi-update nga Seksyon 3.2 "Rehistro sa NVMKEY"

- Gi-update ang mga nota sa NVMCON: Flash Memory Control Register (tan-awa ang Register 3-1)

- Daghang mga update ang gihimo sa tibuok Seksyon 4.0 "Run-Time Self-Programming (RTSP)"

- Ang ubang mga menor de edad nga pag-update sama sa lengguwahe ug pag-format sa mga update gilakip sa tibuuk nga dokumento

Rebisyon E (Oktubre 2018)

Kini nga rebisyon naglakip sa mosunod nga mga update:

- Gidugang Exampug 2-2, Exampug 4-2, Example 4-6 ug Exampsa 4-9

- Gidugang ang Seksyon 4.5.4 "Row Programming Gamit ang RAM Buffer"

- Gi-update nga Seksyon 1.0 "Introduction", Seksyon 3.3 "NVM Address Registers", Seksyon 4.0 "Run-Time Self-Programming (RTSP)" ug Seksyon 4.5.3 "Single Row Programming Example ”

- Gi-update nga Register 3-1

- Gi-update nga Exampsa 4-7

- Gi-update nga Talaan 5-1

Rebisyon F (Nobyembre 2021)

Gidugang ang Seksyon 3.2.1 "Pagpugong sa mga Pag-undang".

Gi-update nga Exampug 3-1, Exampug 4-1, Exampug 4-2, Exampug 4-5, Exampug 4-6, Exampug 4-7, Exampug 4-8, Example 4-9 ug Exampug 4-10.

Updated Section 3.2 “NVMKEY Register”, Section 4.5.1 “Erasing One Page of Flash”, Section 4.5.3 “Single Row Programming Example” ug Seksyon 4.6.1 “Configuration Register Write Algorithm”.

Matikdi ang mosunod nga mga detalye sa feature sa pagpanalipod sa code sa mga produkto sa Microchip:

- Ang mga produkto sa Microchip nakab-ot ang mga detalye nga anaa sa ilang partikular nga Microchip Data Sheet.

- Nagtuo ang Microchip nga ang pamilya sa mga produkto niini luwas kung gigamit sa gituyo nga paagi, sulod sa mga detalye sa pag-operate, ug sa ilawom sa normal nga mga kondisyon.

- Ang mga mithi sa Microchip ug agresibo nga nanalipod sa mga katungod sa intelektwal nga kabtangan niini. Ang mga pagsulay sa paglapas sa mga bahin sa pagpanalipod sa code sa produkto sa Microchip hugot nga gidili ug mahimong makalapas sa Digital Millennium Copyright Act.

- Bisan ang Microchip o bisan unsang ubang tiggama sa semiconductor dili makagarantiya sa seguridad sa code niini. Ang pagpanalipod sa code wala magpasabut nga gigarantiyahan namon ang produkto nga "dili mabuak". Ang pagpanalipod sa code kanunay nga nag-uswag. Gipasalig sa Microchip ang padayon nga pagpaayo sa mga bahin sa pagpanalipod sa code sa among mga produkto

Kini nga publikasyon ug ang impormasyon dinhi mahimong gamiton lamang sa mga produkto sa Microchip, lakip ang pagdesinyo, pagsulay, ug paghiusa sa mga produkto sa Microchip sa imong aplikasyon. Ang paggamit niini nga impormasyon sa bisan unsang laing paagi naglapas niini nga mga termino. Ang impormasyon bahin sa mga aplikasyon sa device gihatag lamang para sa imong kasayon ug mahimong mapulihan sa mga update. Imong responsibilidad ang pagsiguro nga ang imong aplikasyon nagtagbo sa imong mga detalye. Kontaka ang imong lokal nga opisina sa pagbaligya sa Microchip alang sa dugang nga suporta o, pagkuha og dugang nga suporta sa https://www.microchip.com/en-us/support/design-help/client-supportservices.

KINI NGA IMPORMASYON GIHATAG SA MICROCHIP "AS IS". ANG MICROCHIP WALAY MGA REPRESENTASYON O WARRANTY SA BISAN UNSANG KLASE MAPASABOT O GIPASULOD, GISULAT O ORAL, STATUTORY O UBAN PA, MAY KALAMBOAN SA IMPORMASYON LAKIP APAN DILI LIMITADO SA BISAN UNSANG GIPASABOT NGA WARRANTY SA DILI PAGPATUMAN, PAGPATUMAN, PAGPATUMAN, MGA WARRANTY NGA MAY labot sa KINI NGA KONDISYON, KALIDAD, O PERFORMANCE. BISAN WALA MAN ANG MICROCHIP MAHIMONG TUBAG ALANG SA BISAN UNSANG INDIRECT, ESPESYAL, PUNITIVE, INCIDENTAL, O KONSEQUENTIAL NGA PAGKAWAL, KADOT, GASTO, O GASTO SA BISAN UNSANG KLASE NGA MAY MALAIT SA IMPORMASYON O PAGGAMIT KINI, BISAN UNSAY HINUNGDANON, BISAN KON NAHIMO ANG POSIBILIDAD O ANG MGA KADOT MAHITABO. HANGTOD SA KATAPUSAN NGA GITUGOT SA BALAOD, ANG TOTAL LIABILIDAD SA MICROCHIP SA TANANG MGA PANG-ANGKON SA UNSANG PAAGI NGA MAY KAlambigitan SA IMPORMASYON O ANG PAGGAMIT NIINI DILI MOLABAW SA KANTOS SA BAYRAN, KUNG MAY UNSA, NGA IMONG GIBAYAD DIREKTA SA MICROCHIP ALANG SA IMPORMASYON.

Ang paggamit sa mga gamit sa Microchip sa suporta sa kinabuhi ug/o mga aplikasyon sa kaluwasan hingpit nga naa sa peligro sa pumapalit, ug ang pumapalit miuyon nga depensahan, bayran ug huptan nga dili makadaot ang Microchip gikan sa bisan unsa ug tanan nga mga kadaot, pag-angkon, mga demanda, o mga gasto nga resulta sa ingon nga paggamit. Wala’y mga lisensya nga gihatag, sa tinuud o kung dili, sa ilawom sa bisan unsang mga katungod sa intelektwal nga kabtangan sa Microchip gawas kung gipahayag.

Alang sa kasayuran bahin sa Mga Sistema sa Pagdumala sa Kalidad sa Microchip, palihug bisitaha www.microchip.com/quality.

Mga marka sa pamatigayon

Ang Microchip nga ngalan ug logo, ang Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, ug XMEGA kay mga rehistradong trademark sa Microchip Technology Incorporated sa USA ug ubang mga nasud. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, Ang SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, ug ZL mga rehistradong trademark sa Microchip Technology Incorporated sa USA

Kasikbit nga Key Suppression, AKS, Analog-for-the-Digital Age, Bisan unsang Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DEM Average Matching , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Parallel, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewAng Span, WiperLock, XpressConnect, ug ZENA mga marka sa Microchip Technology Incorporated sa USA ug uban pang mga nasud.

Ang SQTP usa ka marka sa serbisyo sa Microchip Technology Incorporated sa USA

Ang logo sa Adaptec, Frequency on Demand, Silicon Storage Technology, Symmcom, ug Trusted Time kay mga rehistradong tatak sa Microchip Technology Inc. sa ubang mga nasud.

Ang GestIC usa ka rehistradong marka sa Microchip Technology Germany II GmbH & Co. KG, usa ka subsidiary sa Microchip Technology Inc., sa ubang mga nasud.

Ang tanan nga uban pang mga marka sa pamatigayon nga gihisgutan dinhi mga kabtangan sa ilang mga kompanya.

© 2009-2021, Microchip Technology Incorporated ug mga subsidiary niini.

Tanang Katungod Gigahin.

ISBN: 978-1-5224-9314-3

Tibuok Kalibutan nga Pagbaligya ug Serbisyo

AMERIKA

- Opisina sa Kumpanya

2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200

Fax: 480-792-7277

Teknikal nga Suporta: http://www.microchip.com/

suporta Web adres: www.microchip.com - Atlanta

Duluth, GA

Tel: 678-957-9614

Fax: 678-957-1455 - Austin, TX

Tel: 512-257-3370 - Boston

Westborough, MA

Tel: 774-760-0087

Fax: 774-760-0088 - Chicago

Itasca, IL

Tel: 630-285-0071

Fax: 630-285-0075 - Dallas

Addison, TX

Tel: 972-818-7423

Fax: 972-818-2924 - Detroit

Novi, MI

Tel: 248-848-4000 - Houston, TX

Tel: 281-894-5983 - Indianapolis

Noblesville, IN

Tel: 317-773-8323

Fax: 317-773-5453

Tel: 317-536-2380 - Los Angeles

Mission Viejo, CA

Tel: 949-462-9523

Fax: 949-462-9608

Tel: 951-273-7800 - Raleigh, NC

Tel: 919-844-7510 - New York, NY

Tel: 631-435-6000 - San Jose, CA

Tel: 408-735-9110

Tel: 408-436-4270 - Canada - Toronto

Tel: 905-695-1980

Fax: 905-695-2078

ASIA/PACIFIC

- Australia - Sydney

Tel: 61-2-9868-6733 - China - Beijing

Tel: 86-10-8569-7000 - China - Chengdu

Tel: 86-28-8665-5511 - China - Chongqing

Tel: 86-23-8980-9588 - China - Dongguan

Tel: 86-769-8702-9880 - China - Guangzhou

Tel: 86-20-8755-8029 - China - Hangzhou

Tel: 86-571-8792-8115 - China - Hong Kong SAR

Tel: 852-2943-5100 - China - Nanjing

Tel: 86-25-8473-2460 - China - Qingdao

Tel: 86-532-8502-7355 - China - Shanghai

Tel: 86-21-3326-8000 - China - Shenyang

Tel: 86-24-2334-2829 - China - Shenzhen

Tel: 86-755-8864-2200 - China - Suzhou

Tel: 86-186-6233-1526 - China - Wuhan

Tel: 86-27-5980-5300 - China – Xian

Tel: 86-29-8833-7252 - China - Xiamen

Tel: 86-592-2388138 - China - Zhuhai

Tel: 86-756-3210040 - India - Bangalore

Tel: 91-80-3090-4444 - India - Bag-ong Delhi

Tel: 91-11-4160-8631 - India - Pune

Tel: 91-20-4121-0141 - Japan - Osaka

Tel: 81-6-6152-7160 - Japan - Tokyo

Tel: 81-3-6880-3770 - Korea – Daegu

Tel: 82-53-744-4301 - Korea - Seoul

Tel: 82-2-554-7200 - Malaysia - Kuala Lumpur

Tel: 60-3-7651-7906 - Malaysia – Penang

Tel: 60-4-227-8870 - Pilipinas – Manila

Tel: 63-2-634-9065 - Singapore

Tel: 65-6334-8870 - Taiwan - Hsin Chu

Tel: 886-3-577-8366 - Taiwan - Kaohsiung

Tel: 886-7-213-7830 - Taiwan - Taipei

Tel: 886-2-2508-8600 - Thailand - Bangkok

Tel: 66-2-694-1351 - Vietnam – Ho Chi Minh

Tel: 84-28-5448-2100

EUROPE

- Austria - Wels

Tel: 43-7242-2244-39

Fax: 43-7242-2244-393 - Denmark – Copenhagen

Tel: 45-4485-5910

Fax: 45-4485-2829 - Finland - Espoo

Tel: 358-9-4520-820 - France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 - Alemanya - Garching

Tel: 49-8931-9700 - Alemanya - Haan

Tel: 49-2129-3766400 - Alemanya - Heilbronn

Tel: 49-7131-72400 - Alemanya - Karlsruhe

Tel: 49-721-625370 - Alemanya - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44 - Alemanya - Rosenheim

Tel: 49-8031-354-560 - Italy - Milan

Tel: 39-0331-742611

Fax: 39-0331-466781 - Italy - Padova

Tel: 39-049-7625286 - Netherlands – Drunen

Tel: 31-416-690399

Fax: 31-416-690340 - Norway – Trondheim

Tel: 47-7288-4388 - Poland - Warsaw

Tel: 48-22-3325737 - Romania – Bucharest

Tel: 40-21-407-87-50 - Espanya - Madrid

Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 - Sweden - Gothenberg

Tel: 46-31-704-60-40 - Sweden - Stockholm

Tel: 46-8-5090-4654 - UK – Wokingham

Tel: 44-118-921-5800

Fax: 44-118-921-5820

Mubo nga sulat:

Kini nga seksyon sa manwal nga pakisayran sa pamilya gituyo aron magsilbing komplemento sa mga sheet sa datos sa aparato. Depende sa variant sa device, kining manwal nga seksyon mahimong dili magamit sa tanang dsPIC33/PIC24 device. Palihog konsultaha ang nota sa sinugdanan sa “Flash Program Memory” nga kapitulo sa kasamtangan nga device data sheet aron masusi kon kini nga dokumento nagsuporta sa device nga imong gigamit.

Ang mga data sheet sa device ug mga seksyon sa manwal nga pakisayran sa pamilya anaa alang sa pag-download gikan sa Microchip sa Tibuok Kalibutan Website sa: http://www.microchip.com.

Mga Dokumento / Mga Kapanguhaan

|

MICROCHIP PIC24 Flash Programming [pdf] Giya sa Gumagamit PIC24 Flash Programming, PIC24, Flash Programming, Programming |

|

MICROCHIP PIC24 Flash Programming [pdf] Giya sa Gumagamit PIC24 Flash Programming, PIC24, Flash Programming |